## Product! **CBC921 PMRTC**

**Data Brief**

### Real-Time Clock/Calendar with Power Manager and Battery Charger

#### **Features**

- Ultra-low power Real-Time Clock (RTC) with power-fail detect and battery management

- Low power timer and power manager extend run time in battery-powered systems

- Controls 4.1V rechargeable micro-batteries and 3.2V rechargeable coin cells and supercaps; no off-chip components required for battery charger

- Buck charge pump supply extends backup battery life:

20nA RTC using internal RC oscillator 50nA RTC using crystal oscillator

- Counters for hundredths, seconds, minutes, hours, date, month, year, century, and weekdays based on a 32.768KHz crystal oscillator or internal RC oscillator

- Automatic leap year calculation

- Alarm capability on all counters

- Two configurable multi-use outputs for interrupts, output clock, and managing sleep mode of external devices

- 64 bytes of RAM

- Internal temperature measurement with 10-bit ADC enables oscillator temperature compensation

- Advanced crystal calibration to ± 1 ppm

- Ultra-low Iq VIN POR circuit (< 25nA)

- Fixed indicators for PGOOD, charging current on, and charging disabled

- Temperature range -40°C to +85°C

#### **Applications**

- Power bridging to provide uninterruptible RTC function during exchange of main batteries.

- **Consumer appliances** that have real-time clocks; provides switchover power from main supply to backup battery.

- Ultra-Low Power Timer using only 20nA

- Wireless sensors and RFID tags and other powered, low duty cycle applications.

- Business and industrial systems such as: network routers, point-of-sale terminals, singleboard computers, test equipment, multi-function printers, industrial controllers, and utility meters.

- Reliable system timekeeping

- Battery-powered devices

- Internet of Things, portable devices

- Daily alarms

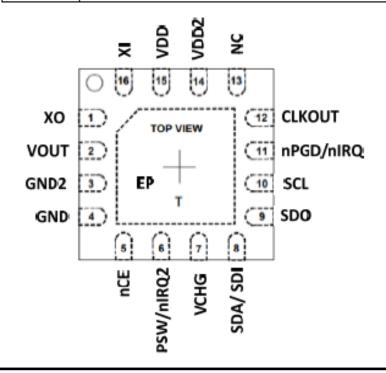

3mm x 3mm x 0.5mm 16-pin MLPQ Package

#### General Description

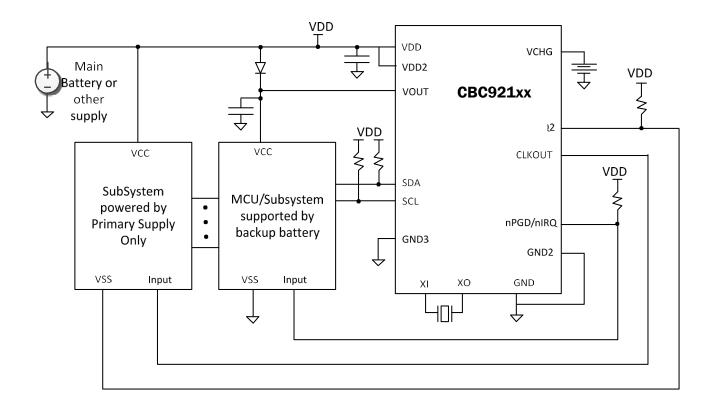

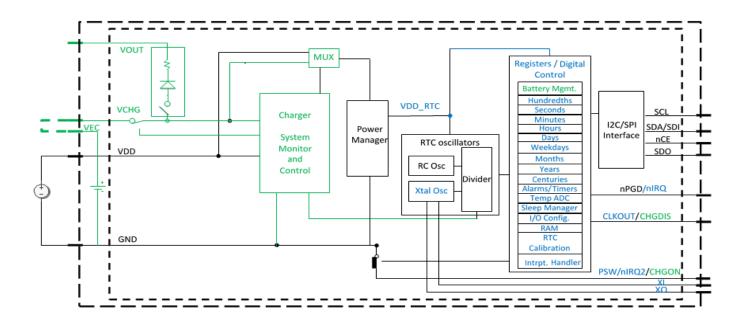

The CBC921xx combines a real-time clock (RTC) with a backup battery charger and other power management features. In the event of an outage of the primary power source, automatic switchover to the backup battery enables extended timekeeping and optionally provides power to external devices to maintain their operation during the power outage.

In normal operation the RTC function is supported by a primary power source, which can be a battery cell, multiple alkaline batteries, or a regulated power supply ranging from 2.85V to 5.5V. The backup battery is charged with a temperature-compensated voltage derived from the primary voltage source. The backup battery charging is refreshed with a configurable schedule and temperature-dependent duty cycle, both of which are designed to increase service life of the backup battery while minimizing power consumption from the main power source.

The circuit can be used in applications to provide an uninterrupted continuous time clock, calendar function, and time-based interrupts or alarms for wake up from sleep to active mode operation with adjustable intervals to save power in the overall system.

The power management has a low quiescent current and high efficiency for backup battery charging. The RTC circuit has very low guiescent current to extend the RTC run time. The RTC has 2ppm accuracy for clock, calendar, alarm, clock outputs, and interrupt functions. An open drain internal power switch is controlled by interrupts and a sleep manager to facilitate power saving by disconnecting main power from external devices according to user-defined schedules.

## **CBC921 Typical Application Schematic**

## **Block Diagram**

## **Pin Descriptions**

| Pin<br># | PM-<br>RTC<br>Pin | PMFC   | PM SPI | RTC PC        | RTC<br>SPI   | Pin Type                                                                                                                                                                                                            | Pin Function<br>(for PM-RTC versions with PC or SPI)                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------|--------|--------|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | ХО                | NC     | NC     | хо            | ХО           | Analog<br>output<br>(high-Z)                                                                                                                                                                                        | Crystal oscillator connection high-impedance node. Minimize trace length between the crystal and the I.C.                                                                                                                                                                                                                                                                                                      |

| 2        | VOUT              | VOUT   | VOUT   | NC            | NC           | Supply<br>Output                                                                                                                                                                                                    | Output voltage providing bias to external circuits in backup mode only. Enabled by VOUTEN register bit. A high-resistance switch and series diode feeding this pin limit the output current and, protect the battery.                                                                                                                                                                                          |

| 3        | GND2              | GND2   | GND2   | GND2          | GND2         | ground                                                                                                                                                                                                              | This pin must be connected to ground (GND).                                                                                                                                                                                                                                                                                                                                                                    |

| 4        | GND               | GND    | GND    | GND           | GND          | ground                                                                                                                                                                                                              | Ground                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5        | υCE               | GND3   | oCE    | GND3          | υCE          | Digital Input<br>(CMOS)                                                                                                                                                                                             | Chip <u>Enable</u> for SPI. Connect this pin to ground when using the I <sup>2</sup> C version.                                                                                                                                                                                                                                                                                                                |

| 6        | PSW/<br>nIRQ2     | oCHGON | nCHGON | PSW<br>/nIRQ2 | PSW<br>/nRQ2 | Output -<br>Open Drain                                                                                                                                                                                              | Configurable open-drain output. This pin has a low-resistance switch to ground which can be connected to the ground return of external devices to switch power to those devices. If no interrupt is enabled, PSWEN_WAKE=1, and no other function is configured by the Control Register 2, this pin has the default function of indicating with an active low output if the battery is currently being charged. |

| 7        | VCHG              | VCHG   | VCHG   | NC            | NC           | Supply<br>In/Out                                                                                                                                                                                                    | Regulated voltage source output for backup battery charging. Power supply input in backup mode. Connect a battery or other energy storage device between this pin and GND.                                                                                                                                                                                                                                     |

| 8        | SDA/<br>SDI       | SDA    | SDI    | SDA           | SDI          | Serial data input/output for PC version. Serial data in Digital I/O - version. A pull-up resistor is needed on this bus.  Open Drain between 5 KΩ and 100 KΩ is recommended dependency of the serial communication. |                                                                                                                                                                                                                                                                                                                                                                                                                |

# **Pin Descriptions (continued)**

|    |               |        |        |               |               |                             | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----|---------------|--------|--------|---------------|---------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9  | SDO           | NC     | SDO    | NC            | SDO           | Digital<br>Output<br>(CMOS) | Serial data output for SPI version. Leave this pin open when using I <sup>2</sup> C version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 10 | SCL           | SCL    | SCL    | SCL           | SCL           | Digital Input<br>(CMOS)     | P <sup>2</sup> C clock/SPI clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 11 | aPGD<br>/alBQ | nESD   | nPGD   | aPSD/<br>aBQ. | aPSD/<br>alBQ | Output -<br>Open Drain      | Configurable PGOOD indicator and interrupt 1 output. Initially functions as a power good signal, going to an active-low state when the SC63xxx I/O's are ready. At this time, the pin function may be reconfigured by writing to the OUT1S bit through the serial port. Otherwise, this pin will follow the PGOOD register bit, staying active-low until VDD falls below the POR falling threshold. A pull-up resistor to VDD is required to use this pin. Use a maximum value of 200 $M\Omega$ , but a lower value may be needed for higher frequency output selections. |  |

| 12 | CLK           | CHGDIS | CHGDIS | CLKOUT        | CLKOUT        | Digital<br>Output -         | Programmable CMOS clock output. Until configured by the<br>clock output control register, this pin has the default function of                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|    |               |        |        |               |               | CMOS                        | indicating (with output high) if charging is disabled by either<br>the CHGOFF or CHGRST register bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 13 | NC            | NC     | NC     | NC            | NC            | open                        | Unused pin, not connected to the I.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 14 | VDD2          | VDD2   | VDD2   | VDD2          | VDD2          | Supply                      | This pin must be connected to the VDD pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 15 | VDD           | VDD    | VDD    | VDD           | VDD           | Supply                      | Main power source input. Can be connected to the main battery or another voltage source. Place decoupling capacitor of at least 0.1 uF between VDD and GND close to the I.C.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 16 | ΧI            | NC     | NC     | ΧI            | ΧI            | Analog<br>input             | Crystal oscillator input, high-impedance node. Minimize trace<br>length between the crystal and the I.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 17 | EP            | EP     | EP     | EP            | EP            | Exposed<br>Pad              | Connect the exposed pad to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

## **Absolute Maximum Ratings**

| Parameter                                      | Symbol                                   | Value                          | Units |

|------------------------------------------------|------------------------------------------|--------------------------------|-------|

| External Supply Input (VDD)                    | V <sub>DD</sub> to V <sub>GND</sub>      | -0.3 to +6.0                   | V     |

| Battery Connection Pin (VCHG)                  | V <sub>CHG</sub> to V <sub>GND</sub>     | -0.3 to +4.15                  | V     |

| Supply Output Voltage Pin (VOUT)               | V <sub>OUT</sub> to V <sub>GND</sub>     | -0.3 to +6.0                   | V     |

| XI, XO pins in VDD Mode                        | V <sub>XT_VDD</sub> to V <sub>GND</sub>  | -0.3 to V <sub>DD</sub> +0.3   | V     |

| XI, XO pins in Backup Mode                     | $V_{XT\_BAT}$ to $V_{GND}$               | -0.3 to V <sub>CHG</sub> + 0.3 | V     |

| VDD2 pin to VDD pin                            | V <sub>DD2</sub> to V <sub>DD</sub>      | -0.3 to +0.3                   | V     |

| GND2 pin to GND pin                            | $V_{GND2}$ to $V_{GND}$                  | -0.3 to +0.3                   | V     |

| SCL, SDA/SDI, PSW/nIRQ2, nPGD/IRQ, nCE pins    | V <sub>io1</sub> to V <sub>GND</sub>     | -0.3 to +6.0                   | V     |

| CLKOUT and SDO pins, in Backup and VDD Modes   | V <sub>IO2</sub> to V <sub>GND</sub>     | -0.3 to V <sub>DD</sub> +0.3   | V     |

| PSW/nIRQ2pin current                           | PSW                                      | 200                            | mA    |

| ESD Protection Level (HBM), VCHG pin (1)       | V <sub>CHG_ESD</sub> to V <sub>GND</sub> | TBD                            | kV    |

| ESD Protection Level (HBM), all other pins (1) | V <sub>IO_ESD</sub> to V <sub>GND</sub>  | 2                              | kV    |

| Operating Temperature                          | T,                                       | -40 to +85                     | °C    |

| Storage Temperature                            | T <sub>stg</sub>                         | -65 to +150                    | °C    |

Notes:

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

(1): Tested according to JEDEC standard JESD22-A114-B. No ESD protection is guaranteed on the VCHG pin.

#### **Thermal Characteristics**

| Parameter                        | Symbol           | Value | Units |

|----------------------------------|------------------|-------|-------|

| Thermal Impedance <sup>(2)</sup> | R <sub>eva</sub> | 50    | °C/W  |

Notes:

(2): Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB per JESD51 standards.

#### **Electrical Characteristics**

Unless otherwise specified:  $T_1 < 85^{\circ}C_{\infty} = 40^{\circ}C < T_A < +85^{\circ}C$ , VDD = 3.6 V, 1uF VDD to GND. Typical values are for  $T_A = +25^{\circ}C$

|                                                                  |                           | T <sub>A</sub> <+85 °C, VDD = 3.6 V, 1uF VDD to GND. Typid                                                                                                                                                                        |                        |      |      |       |

|------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|-------|

| Parameter                                                        | Symbol                    | Conditions                                                                                                                                                                                                                        | Min                    | Тур. | Max. | Units |

| Supply Range                                                     |                           |                                                                                                                                                                                                                                   |                        |      |      |       |

| VDD Supply Voltage Range                                         | Vdd                       |                                                                                                                                                                                                                                   | V <sub>DORusioin</sub> |      | 5.5  | V     |

| VDD Power-on Reset Rising<br>Threshold                           | V <sub>POR rising</sub>   | Backup to VDD mode entry threshold                                                                                                                                                                                                |                        | 2.7  | 2.85 | V     |

| VDD Power-on Reset Falling<br>Threshold                          | V <sub>BOR folling</sub>  | Battery backup entry threshold                                                                                                                                                                                                    | 2                      |      |      | ٧     |

| VDD Power-on Reset<br>Threshold Hysteresis                       | V <sub>BOR bysterie</sub> | VgoR ining - VgoR falling                                                                                                                                                                                                         | 9                      | 125  | 170  | mV    |

| VDD POR rising indicator<br>delay, from cutoff mode              | Td <sub>gcRousett</sub>   | Measured from VDD crossing Vacation to the falling edge of the aPGD/aIRO pin, VCHG=2.5V                                                                                                                                           |                        | 300  |      | øs.   |

| VDD POR rising indicator<br>delay, from backup mode              | Td <sub>BCD beckup</sub>  | Measured from VDD crossing V <sub>2013 in int</sub> to the falling edge of the <u>aPGD/aIRO</u> pin, VCHG=4V                                                                                                                      |                        | 80   |      | ms    |

| Battery Charging Delay<br>Time                                   | Td <sub>CUC wing</sub>    | Measured from falling edge of the nPGD/nIBQ pin to rising edge of CHG pin.                                                                                                                                                        |                        | 40   |      | øs.   |

| VOUT Cut-in Time Delay                                           | Tdyout ming               | Measured from VDD crossing Vacasiums<br>threshold to the VOUT switch turn-on                                                                                                                                                      |                        | 1    |      | , ms  |

| Supply Currents                                                  |                           |                                                                                                                                                                                                                                   |                        |      |      |       |

| VCHG Supply Current, RC<br>Mode, with Cutoff Monitor<br>Inactive | Ichg_Rc4                  | Includes RTC operating in RC mode. 4.1V<br>version. VCHG =4.1V. VDD=0 V.                                                                                                                                                          |                        | 20   |      | Aα    |

| VCHG Supply Current, RC<br>Mode, with Cutoff Monitor<br>Inactive | leng_rez                  | Includes RTC operating in RC mode. 3.2V  version.  VCHG = 3.2V. VDD=0V.                                                                                                                                                           |                        | 60   |      | Aα    |

| VCHG Supply Current, XT<br>Mode, with Cutoff Monitor<br>Inactive | Існа_хын                  | Includes RTC operating in XTAL mode. 4.1V  version.  VCHG = 4.1V. VDD=0V.,                                                                                                                                                        |                        | 50   |      | аA.   |

| VCHG Supply Current, XT<br>Mode, with Cutoff Monitor<br>Inactive | ICHG_Xwiii                | Includes RTC operating in XTAL mode. 3.2V  version.  VCHG = 3.2V. VDD=0V.                                                                                                                                                         |                        | 150  |      | ρA    |

| VCHG Supply Current, XT<br>Mode, with Cutoff Monitor<br>Active   | ICHG. XmMon               | Includes RTC operating in XTAL mode. 4.1V<br>yersion only. VCHG =4.1V, VDD=0V                                                                                                                                                     |                        | 350  |      | ρA    |

| VDD Supply Current with<br>Battery Charging                      | <u>ldd</u> churgu         | After POR rising. Excludes battery charging current, but including RTC in <u>Xtal</u> mode. <u>nCE</u> pin held at VDD. SDA/SDI and SCL pins held at VDD or GND. I <sup>2</sup> C bus inactive, other I/O's <u>pat</u> switching. |                        | 4000 |      | σA    |

| VDD Supply Current with<br>Battery Not Charging                  | lddactoen                 | After POR rising. RTC operating in XTAL mode. I <sup>2</sup> C bus inactive. Other I/Q's static. nCE pin held at VDD. SDA/SDI and SCL pins held at VDD or GND. No load on CLKOUT/CHGDIS. Logic outputs high (open-drain).         |                        | 75   |      | υA    |

| VDD Supply Current in<br>Backup Mode                             | lddeses                   | VDD=2.5V                                                                                                                                                                                                                          |                        | 25   |      | ρA    |

| CHG leakage Current, Cutoff<br>Mode                              | I CHOLUMBE                | VHG=2.5V. VDD=0V.<br>4.1V version only                                                                                                                                                                                            |                        | 70   |      | Aga   |

### **Electrical Characteristics**

| Parameter                                | Symbol                 | Conditions                                           | Min.  | Тур.  | Max. | Units   |

|------------------------------------------|------------------------|------------------------------------------------------|-------|-------|------|---------|

| Battery Charger                          |                        |                                                      |       |       |      |         |

| Battery Charger Output<br>Current        | CHGustween             | VCHG=3V                                              |       | 50    |      | J.A.    |

| Battery Charger Output<br>Voltage        | VCHG <sub>4</sub>      | 25°C, VDD> V <sub>BOR raing,MAX</sub> , 4.1V version | 4.025 | 4.075 | 4.1  | ٧       |

| Battery Charger Output<br>Voltage        | VCHG₂                  | 25℃, VDD > Vgog wing Max, 3.2V version               | 3     | 3.1   | 3.2  | ٧       |

| Battery Charger Output<br>Voltage TC     | VCHG <sub>Te4</sub>    | 25℃ to 85℃, 4.1V version                             |       | -2.2  |      | mV/deg€ |

| Battery Charger Output<br>Voltage TC     | VCHG <sub>T∈2</sub>    | 25℃ to 85℃, 3.2V version                             |       | -1.67 |      | mV/degC |

| Battery Cutoff Threshold                 | VCHG <sub>Cutoff</sub> | 4.1V version only                                    | 2.7   | 3     | 3.3  | V       |

| Oscillator                               |                        |                                                      |       |       |      |         |

| RC Oscillator Frequency                  | Fz                     | Ta=25 ℃                                              |       | 256   |      | Hz      |

| RC Oscillator Frequency<br>Accuracy      | F <sub>RC_TOL</sub>    | Without calibration; supply between 2.9V<br>and 5.5V | -4    |       | +4   | 96      |

| Crystal oscillation frequency            | Fen                    |                                                      |       | 32768 |      | Hz      |

| Crystal Internal Load<br>Capacitance     | CL <sub>BT</sub>       |                                                      |       | 2.5   |      | pF      |

| Crystal Negative Resistance              | R <sub>sts</sub>       |                                                      |       | 520   |      | ŔŰ      |

| Interface Logic                          |                        |                                                      |       |       |      |         |

| Logic Input High Threshold               | V <sub>a</sub>         | VDD=5.5V                                             | 1.6   |       |      | ٧       |

| Logic Input Low Threshold                | V <sub>L</sub>         | VDD=2.9V                                             |       |       | 0.4  | ٧       |

| Logic Output High Level                  | V <sub>D</sub>         | CMOS outputs                                         |       |       |      | V       |

| Logic Output Low Level                   | Vn                     | IL<3mA                                               |       |       | 0.4  | ٧       |

| Logic Input Leakage                      | l <sub>elig-kak</sub>  |                                                      |       | < 1   |      | ρA      |

| Switch on-Resistance                     |                        |                                                      |       |       |      |         |

| PSW/nIRQ2/nCHGQN Pull<br>Down Resistance | Rese                   | L lood= 100 mA                                       |       | 4     |      | Ω       |

| VOUT Switch Resistance                   | Recur                  | V <sub>CHG</sub> =4.1V, <u>L_lood</u> =1μA           |       | 1     |      | МΩ      |

| Serial Interface                         |                        |                                                      |       |       |      |         |

| I <sup>2</sup> CClock Frequency          | Fæ                     |                                                      |       |       | 400  | kHz     |

| SPI Clock Frequency                      | Fgq                    |                                                      |       |       | 2000 | kHz     |

Note

(1): See chart of charge voltage vs. temperature (Figure 3)

## **Ordering Information**

| Part      |     | Power      |                  | Charge  |

|-----------|-----|------------|------------------|---------|

| Number    | RTC | Management | I/F              | Voltage |

| CBC92100C | Υ   |            | I <sup>2</sup> C |         |

| CBC92100P | Υ   |            | SPI              |         |

| CBC92032C |     | Υ          | I <sup>2</sup> C | 3.2V    |

| CBC92041C |     | Υ          | I <sup>2</sup> C | 4.1V    |

| CBC92032P |     | Υ          | SPI              | 3.2V    |

| CBC92041P |     | Υ          | SPI              | 4.1V    |

| CBC92132C | Υ   | Υ          | I <sup>2</sup> C | 3.2V    |

| CBC92141C | Υ   | Y          | I <sup>2</sup> C | 4.1V    |

| CBC92132P | Υ   | Υ          | SPI              | 3.2V    |

| CBC92141P | Υ   | Υ          | SPI              | 4.1V    |

| CBC92XYYZ Part Numbering |                                        |  |  |  |  |

|--------------------------|----------------------------------------|--|--|--|--|

| X                        | X 1=RTC included, 0=no RTC             |  |  |  |  |

| YY                       | Maximum battery charging voltage (x10) |  |  |  |  |

|                          | 00=no battery management included      |  |  |  |  |

| Z                        | C=I <sup>2</sup> C, P=SPI              |  |  |  |  |